728x90

반응형

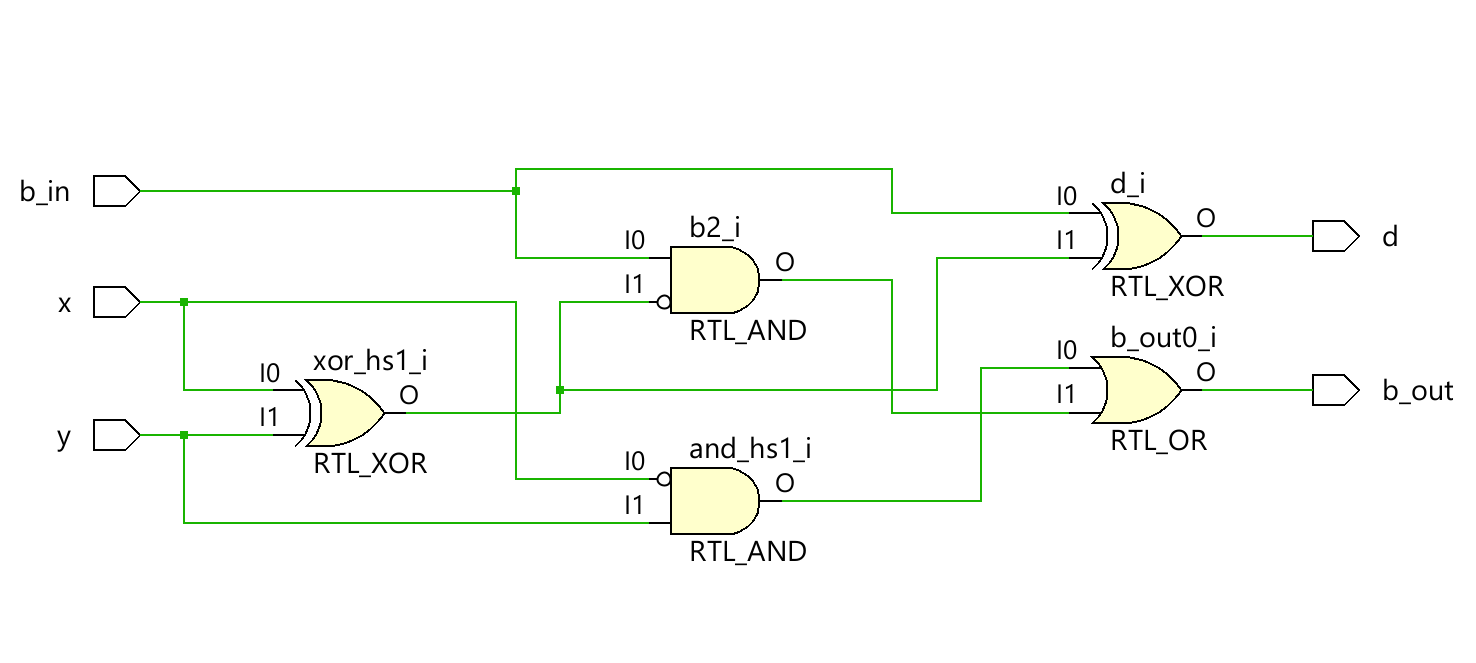

1. Structural Modeling

2. Dataflow Modeling

3. Behavioral Modeling

을 모두 합친 Mixed Modeling입니다.

모든 Modeling시 하나의 스타일만 고집하지 않겠죠.

간단한 1bit 논리동작은 Structural Style로,

비트합 등 Combinational logic 관련은 Dataflow Style로,

FF이 필요한 Sequential logic 관련은 Behavioral Style로

그때 그때 필요한 Style을 Mixing 하는 능력이 곧 코드의 가독성을 높일 것 입니다.

아래는 코드입니다.

Code:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/03/11 14:28:47

// Design Name:

// Module Name: full_subtractor_4

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module full_subtractor_4(x, y, b_in, b_out, d);

input x, y, b_in;

output b_out, d;

reg b_out;

wire b1, b2, d1;

// structural modeling of HS 1.

xor xor_hs1 (d1, x, y);

and and_hs1 (b1, ~x, y);

// dataflow modeling of HS 2.

assign d = b_in ^ d1;

assign b2 = b_in & ~d1;

// behavioral modeling of output OR gate.

always @(b1, b2)

b_out = b1 | b2;

endmodule

주석에 달려있지만, 코드 리뷰를 해보자면

full subtractor는 half subtractor 2개와 1개의 OR gate로 이루어집니다.

HS1은 Structural Style로, HS2는 dataflow Style로 설계했습니다.

wire b1과 b2를 OR로 연결할 때는 always block을 사용하여 behavioral Style을 이용했습니다.

728x90

반응형

'Verilog HDL > 2. Verilog Practice (연습)' 카테고리의 다른 글

| [DPU] DPU IP Block Design (0) | 2024.03.15 |

|---|---|

| [DSD Week3] Practice1 Prob.2 (0) | 2024.03.12 |

| [full_subtractor] 3. Behavioral Modeling (0) | 2024.03.11 |

| [full_subtractor] 2. Dataflow Modeling (0) | 2024.03.11 |

| [full_subtractor] 1. Structural Modeling (0) | 2024.03.10 |