반응형

요즘 대학이 재밌네요.

드디어 기다리고 기다리던 3학년 디지털 시스템 디자인 (DSD) 듣고 있습니다.

3주차 Practice로 led_driver를 만들어보는 문제입니다.

Prob.1은 오프라인 강의에서 다 만들었고,

Prob.2는 2to1 MUX를 이용해서 같은 동작을 만드는 문제입니다.

코드는 비밀

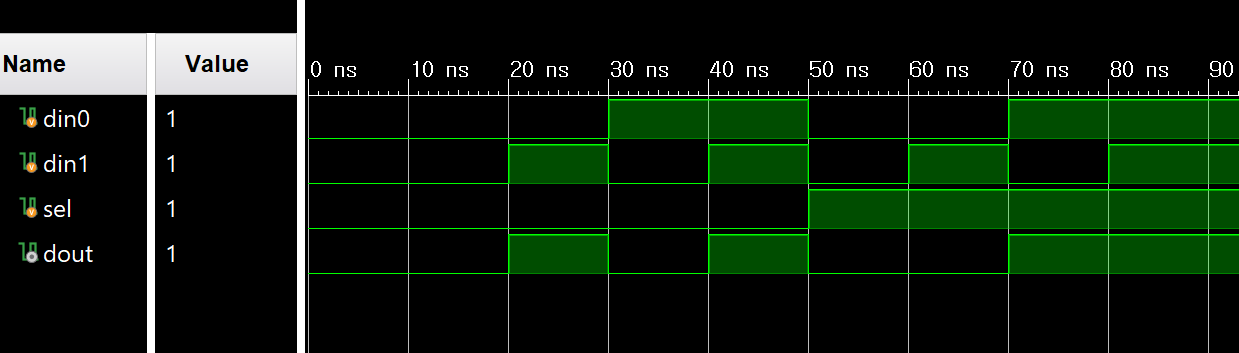

2 to 1 MUX waveform 입니다.

결과가 잘 나왔습니다.

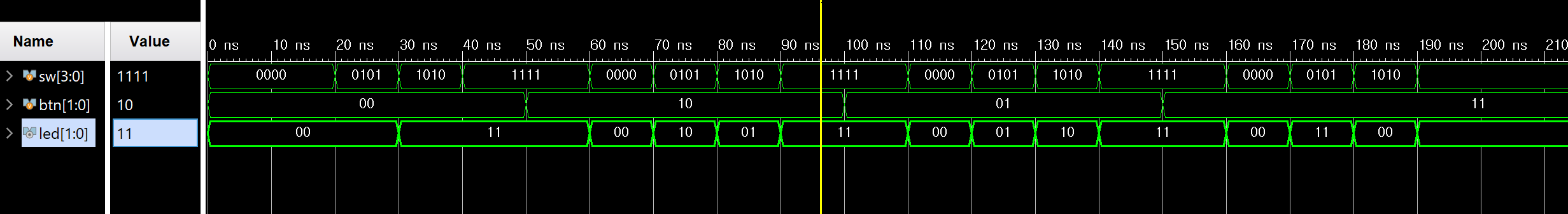

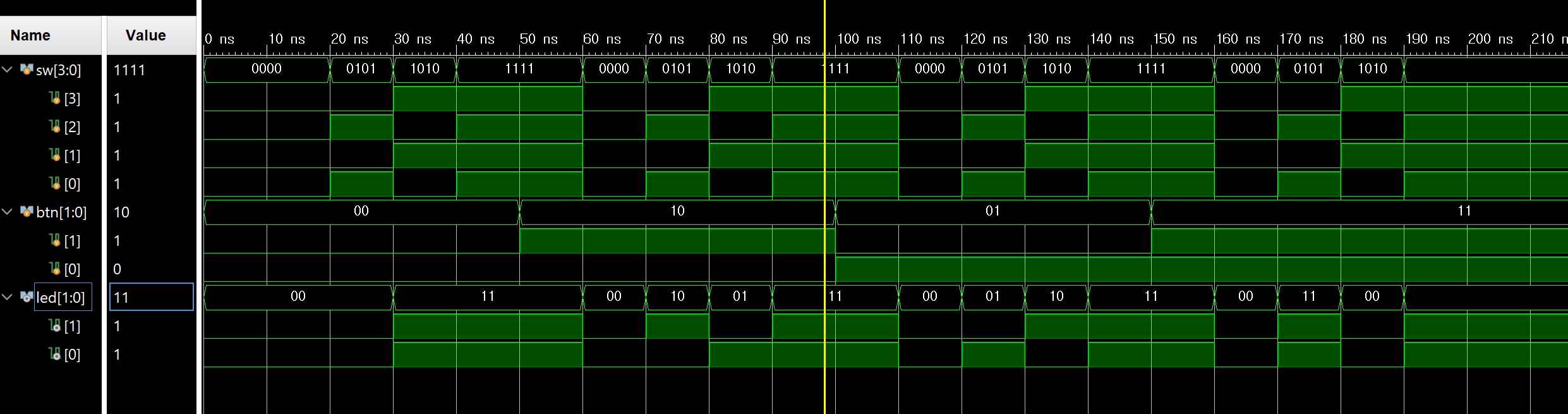

top module의 waveform 입니다.

결과가 잘 나왔는지는 나중에 복습하면서 확인하도록 하겠습니다.

반응형

'Verilog HDL > 2. Verilog Practice (연습)' 카테고리의 다른 글

| [BRAM] BRAM read / write module (0) | 2024.03.27 |

|---|---|

| [DPU] DPU IP Block Design (0) | 2024.03.15 |

| [full_subtractor] 4. Mixed Modeling (0) | 2024.03.11 |

| [full_subtractor] 3. Behavioral Modeling (0) | 2024.03.11 |

| [full_subtractor] 2. Dataflow Modeling (0) | 2024.03.11 |