- net types & variable types

- net types

- 디지털 회로의 연결을 모델링.

- 값 저장 x

- must be driven with data

- variable types

- registers or flip flops 모델링

- 값 저장 o

- C 언어 등의 ==변수== 와 같다.

- net types

- data table

| data | 설명 |

|---|---|

| 0 | 2진수 0 |

| 1 | 2진수 1 |

| z | High impedance |

| x | unknown value |

- 변수의 일반적 구문

<type_name> <size> <variable_name> = <value>;- - type 선언 - ` integer example = 100; `

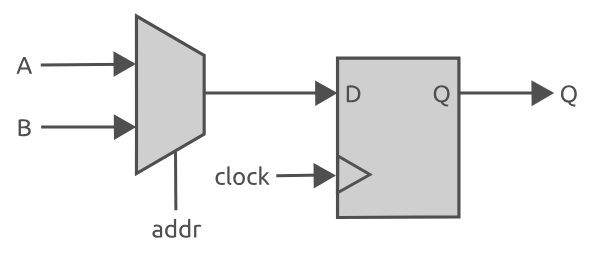

Net Types in Verilog

다른 컴포넌트 사이의 물리적 연결 표현

can not be used to store data values or drive data

위 그림에서 mux의 output을 ff의 input에 연결.

- 컴포넌트 간의 물리적 연결 => net types

일반적으로 wire type 구동 시 continuous assignment 이용

assign키워드// 상수 0을 net type 지정 (assign 키워드 이용) assign a = 1'b0;

always blocks 에서는 net types ==사용 불가==

Wire Type in Verilog

- 가장 일반적인 net type

- 가장 기본적인 point to point 연결

- 전통적인 회로의 선과 같다.

// single wire 선언

wire a;

// wire형에 데이터 전송 ( assign 사용 )

assign a = c;

assign b = d;wand & wor Types

회로에 기본적인 로직 gate를 삽입

- wand : and gate

- wor : or gate

하나 이상의 신호를 assign 해야 사용 가능

각 assign은 gate에 대한 하나의 입력만 나타내기 때문.

// wand , wor types 선언 wor a; wand b;

// gate에 연결하는 wire 선언

wire c, d, e, f;

// OR 로직의 gate 생성 ( c | d )

assign a = c;

assign a = d;

// AND 로직의 gate 생성 ( e & f )

assign b = e;

assign b = f;- wor, wand type 사용은 추천하지 않음.

tri, triand & trior Types

- wire, wand and wor => tri,triand and trior

- wire, wand and wor과 기능은 완전 동일

- design의 의도를 더 명확하게 보여주기 위해 사용

// tri 선언

tri a;

// high impedance 데이터 전송

assign tri = 1'bz;- 실제로는 거의 사용 x

supply0 & supply1 Types

위 type을 통해 신호를 2진수 0 또는 1의 상수 값에 연결 가능

Vcc, GND 에 연결된 net을 생성.

data를 assign 할 필요 x

// 0b에 연결된 net 생성 supply0 a; // 1b에 연결된 net 생성 supply1 b;

But, 이러한 경우가 거의 없고, 이러한 경우에도 wire이용

- 잘 사용하지 않음.

Variable Types in Verilog

- variable data types => 값을 store

- 값을 assign 하면 다시 할당될 때까지 이 값이 유지

- C 언어의 int, str 등과 유사

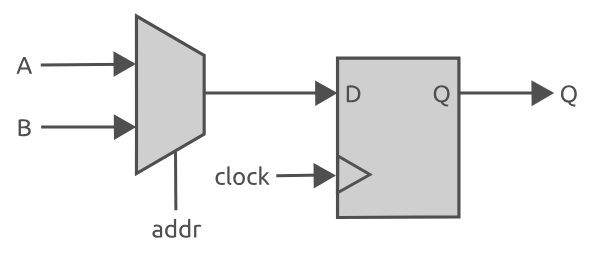

- variable type은 flip flop의 output을 모델링 하는데 사용.

- single bit of data 저장.

- variable type은

always block내에서만 사용 가능 - D FF 코드 예시

always @(posedge clock) q <= d; end

Reg Type in Verilog

가장 많이 사용.

- 값을 저장해야할 때 언제든 사용 가능

보통 flip flops의 행동 모델링에 사용

일부 상황에서는 combinational logic 모델링에 reg 사용

// reg type 선언 reg q;

// basic flip flop 코드

always @(posedge clock)

q <= d;

end

Numeric Variable Types

- 지금까지의 type들은 single bits of data 에 사용됨.

- But, data를 수치로 표현할 수도 있음. (??)

- integer type & real type 구분

Verilog Integer Type

- 가장 일반적인 수치 data

- But, 일반적으로 Port 보다는 모듈 내부 신호에 사용

- integer

- default : 32 bit 2's complement number (2의 보수수)

- 모든 숫자 표현 가능

- assign 시 2진 값이 아닌 숫자 값을 할당.

- reg type도 숫자 값 할당 가능

- integers : constants or loop variables 일 때

- synthesis tool에서는 integer type에서 사용하지 않는 bits를 자동으로 잘라냄.

- 255 정수 선언 => tool이 255를 8bit로 잘라냄.

integer a = 255;

- 255 정수 선언 => tool이 255를 8bit로 잘라냄.

Verilog Real Type

소수점이 있는 숫자 (실수) 를 저장하는 데 사용.

일반적으로 64bit floating point number (부동 소수점 숫자)로 구현

- 직접 합성 불가능.

- 일반적으로 testbenches에서만 real type 사용.

소수점, 과학적 표기법을 사용해 값을 assign 가능4

// real type 선언 real a; // 소수점 표기법을 이용해 할당 a = 2.5; // 과학적 표기법을 이용해 할당 a = 1e-3;

Vector Types in Verilog

numerical types 제외, 나머지 모든 type은 단일 비트로 구성

디지털 회로 내에서 데이터 전송시, data busses를 사용하는 경우가 많음.

Vector types

- 이 type을 사용하여 data busses 생성 가능

- 이를 통해 2개 이상의 bit를 가진 신호 선언 가능

<type> <size> <variable_name>;

<size>

[MSB:LSB] 로 표기

// reg type vector 선언 reg [3:0] a; // 2진수 data assign a = 4'b1010; // 16진수 data assign a = 4'ha; // 10진수 data assign a = 4'd10; // 8진수 data assign a = 4'o12;

Signed and Unsigned Data in Verilog

- 2001 표준 전까지 모든 variable, net types 는 부호가 없는 데이터만 저장할 수 있었음.

- integer type은 항상 부호가 있는 값으로 해석됨.

- 2001표준 이후 signed , unsigned 키워드를 통해 변수가 data를 해석하는 방식 변경 가능.

- type을 signed로 선언하면...

- 2의 보수 숫자로 해석됨 => 음수 할당 가능

- integer type => 기본적으로 signed (부호화)

- reg ,wire types는 필요할 때만 키워드 사용

// reg type 중 signed, unsigned 선언 reg [31:0] a; // unsigned reg signed [31:0] b; // signed

// wire type

wire [31:0] a;

wire signed [31:0] b;

// integer type

integer unsigned a;

integer b;

````

'Verilog HDL > 1. Verilog HDL Basic (문법)' 카테고리의 다른 글

| [Verilog Data Types and Arrays] 4. 예제 풀이 (1) | 2024.01.02 |

|---|---|

| [Verilog Data Types and Arrays] 3. 배열 (1) | 2024.01.02 |

| [Verilog Data Types and Arrays] 1. Data 표현 (1) | 2024.01.02 |

| [Verilog Tutorial] Level-1 Basic Verilog Module 모음 (1) | 2024.01.02 |

| [Basic Verilog Module] 4. 예제 풀이 (1) | 2024.01.02 |