728x90

반응형

문제 링크 : https://hdlbits.01xz.net/wiki/Vector2

문제

32-bit input과 output이 있다.

각 신호는 4-byte씩 끊어서 볼 수 있다. input의 byte 순서를 반대로 output 에 저장하라.

AaaaaaaaBbbbbbbbCcccccccDddddddd => DdddddddCcccccccBbbbbbbbAaaaaaaa

Module 선언

module top_module(

input [31:0] in,

output [31:0] out );//

// assign out[31:24] = ...;

endmodule728x90

내 풀이

module top_module(

input [31:0] in,

output [31:0] out );

assign out [31:24] = in [7:0];

assign out [23:16] = in [15:8];

assign out [15:8] = in [23:16];

assign out [7:0] = in [31:24];

endmodule결과

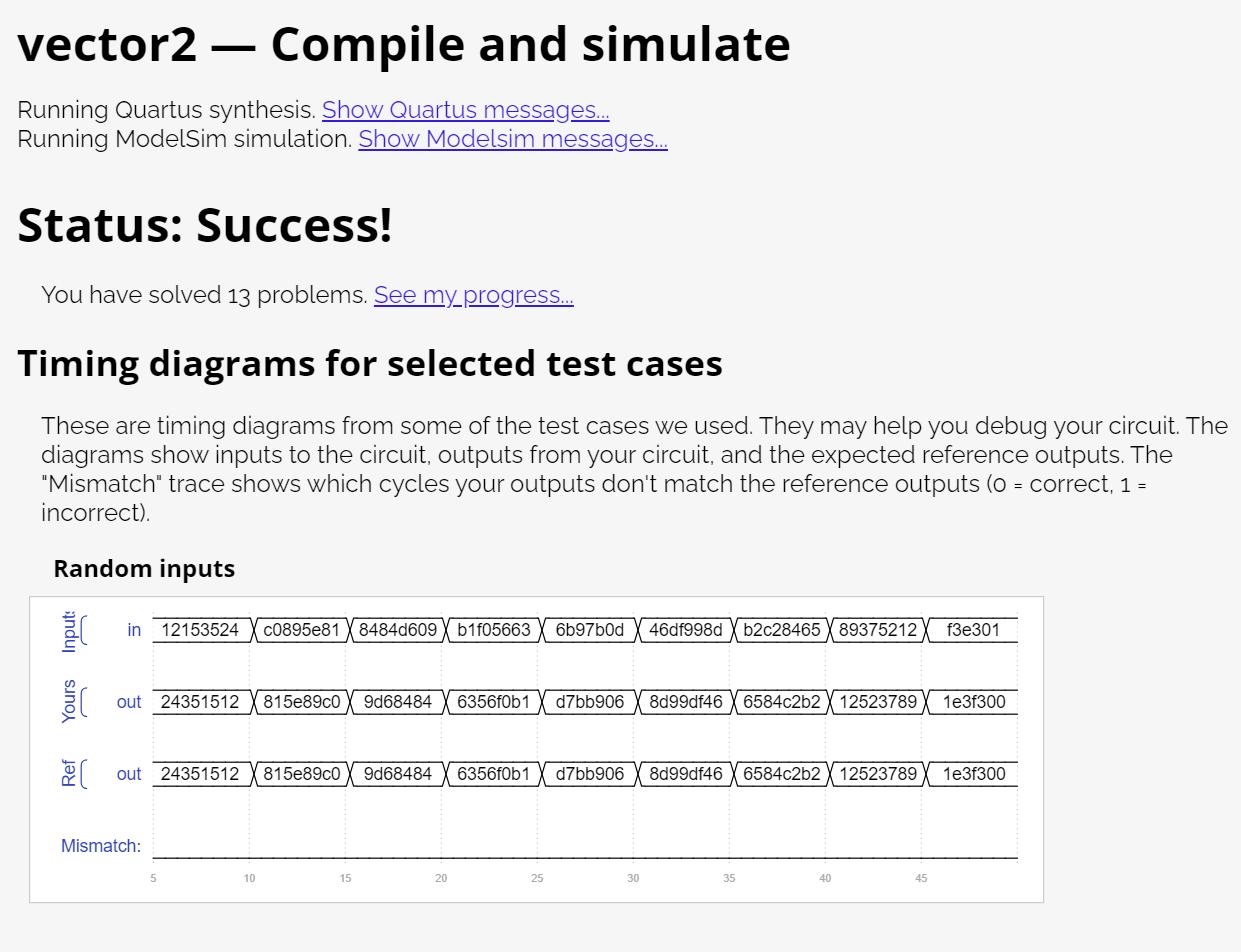

나이스!

반응형

풀이

무식한 풀이로 짰다. 지금은 32bit / 4byte = 4줄이지만, 좀만 늘어나도 무식하게는 못 만들 것이다.

for문을 이용하여 코드를 reusable 하게 설계해보겠다.

module top_module(

input [31:0] in,

output reg [31:0] out

);

genvar i;

generate

for (i = 0; i < 4; i = i + 1) begin : byte_reverser

always @(*) begin

out[8*i +: 8] = in[8*(3-i) +: 8];

end

end

endgenerate

endmodule

for 문을 구조적으로 생성하기 위해 generate 구문을 이용하였다.

for문 옆에 : byte_reverser는 label 이다. 없으면 컴파일 오류 발생.

728x90

반응형

'Verilog HDL > 3. HDLBits (문풀)' 카테고리의 다른 글

| [HDLBits 해설] Vector 1 (0) | 2024.01.22 |

|---|---|

| [HDLBits 해설] Vector0 (0) | 2024.01.18 |

| [HDLBits 해설] 7458 (0) | 2024.01.18 |