반응형

문제 링크 : https://hdlbits.01xz.net/wiki/7458

오늘부터 최소 1문제 이상 업로드 하겠습니다.

문제

설계하십셔.

방법 1. assign으로 output 할당

방법 2. output의 intermediate signals를 wire로 할당

Module 선언

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

endmodule내 풀이

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

wire p1y_1;

wire p1y_2;

wire p2y_1;

wire p2y_2;

assign p1y_1 = (p1a & p1b & p1c);

assign p1y_2 = (p1d & p1e & p1f);

assign p2y_1 = (p2a & p2b);

assign p2y_2 = (p2c & p2d);

assign p1y = (p1y_1 | p1y_2);

assign p2y = (p2y_1 | p2y_2);

endmodule

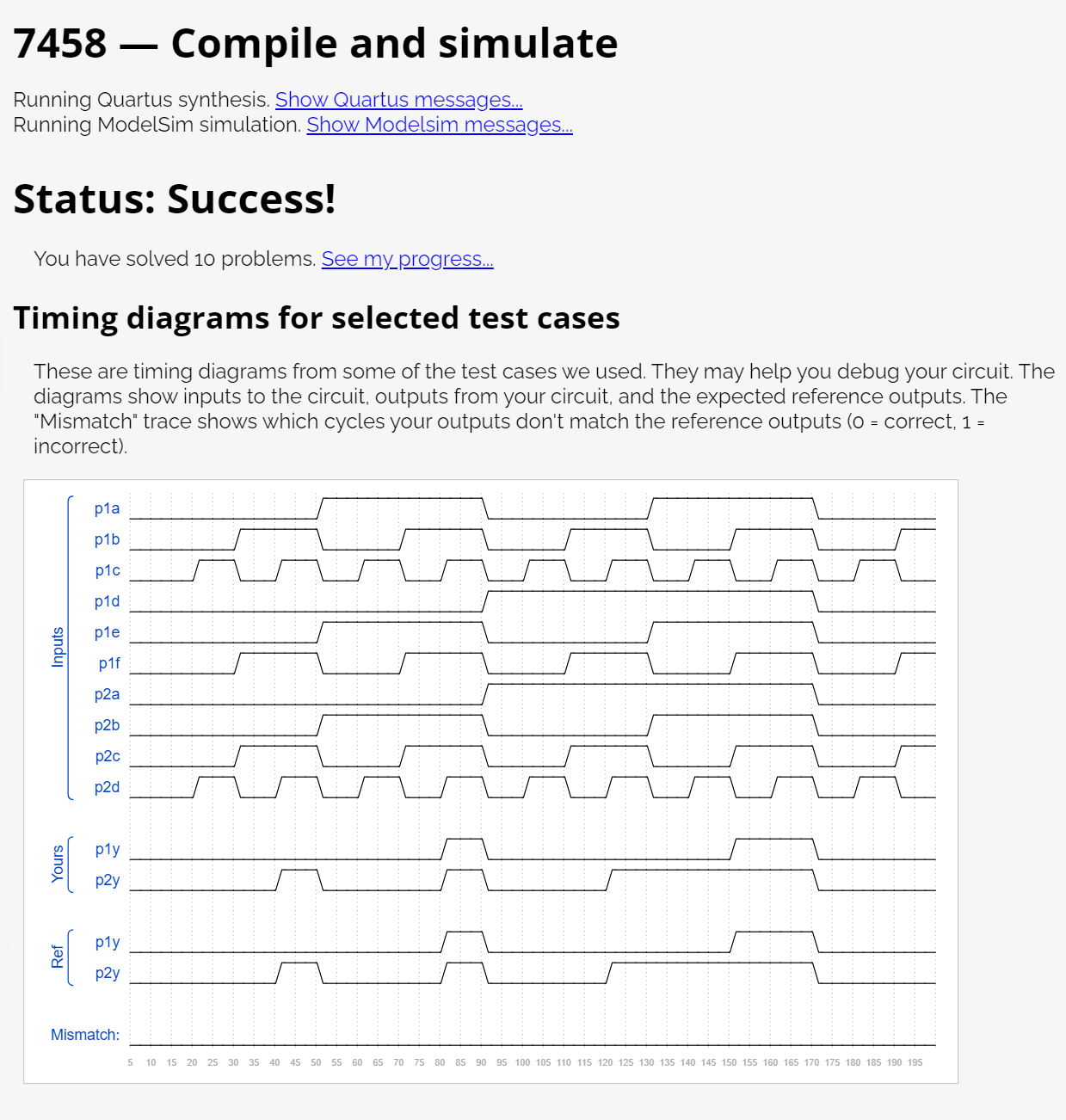

결과

나이스!

풀이

방법 2를 차용해서 p1y, p2y에 들어가는 input을 모두 wire 선언 후 각 논리에 맞게 assign 하였다.

코드는 최소 2줄에서 최대 10줄정도 나올거라던데. 10줄을 다 써버렸다.

2줄 풀이

방법 1을 이용하면 2줄로 코드 길이를 줄일 수 있다.

wire 선언을 안하고 assign 안에 한 줄로 때려박았다.

가독성은 좀 떨어진다.

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = ((p1a & p1b & p1c) | (p1d & p1e & p1f));

assign p2y = ((p2a & p2b) | (p2c & p2d));

endmodule반응형

'Verilog HDL > 3. HDLBits (문풀)' 카테고리의 다른 글

| [HDLBits 해설] Vector 2 (0) | 2024.01.22 |

|---|---|

| [HDLBits 해설] Vector 1 (0) | 2024.01.22 |

| [HDLBits 해설] Vector0 (0) | 2024.01.18 |