728x90

반응형

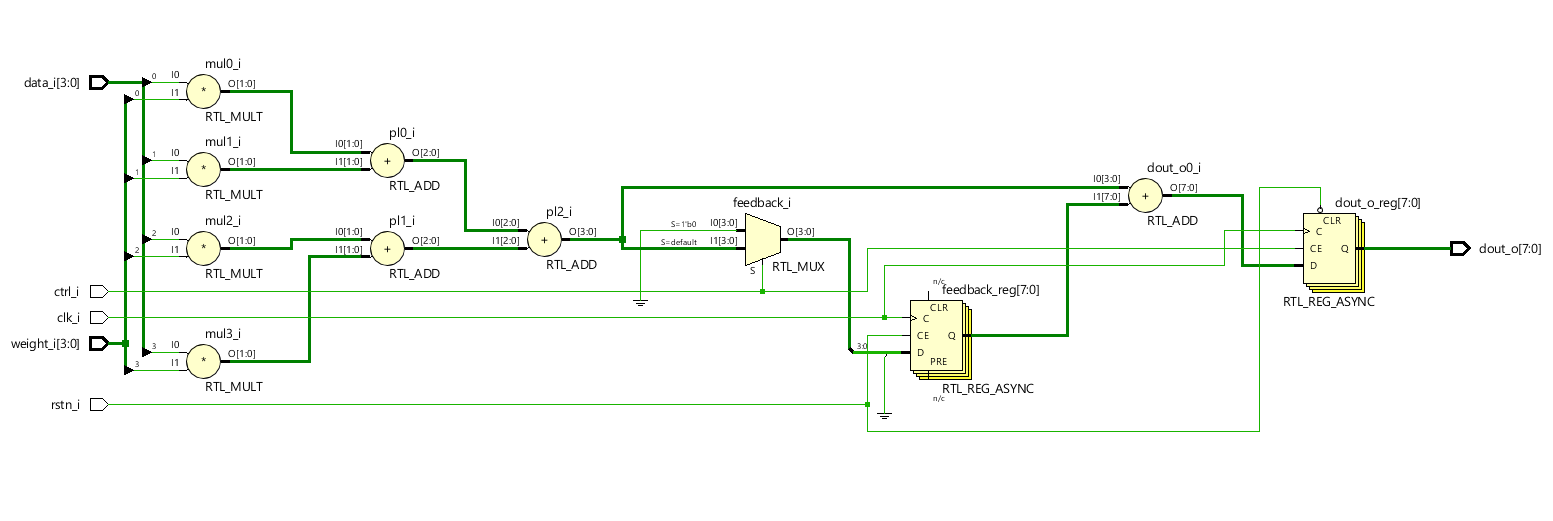

Convolution Design

4bit의 Data input과 4bit의 Weight input을 각 비트마다 곱하고 모든 값을 더하는 Convolution Design이다.

MUX를 도입하여 0일때는 feedback 값이 들어가지 않게, 1일때는 feedback값이 들어가게 설계하였다.

범용적인 NPU 개발기(3) - 아키텍처(2) - convolution

내가 생각한 convolution layer를 수행하기 위한 아키텍처는 2가지가 있는데 한가지는 구현이 쉽지만 효율이 떨어질 것으로 예상되는 것이고 다른 하나는 효율이 좋지만 구현이 어려울 것으로 예상

velog.io

위 게시글을 레퍼런스하여 설계하였다.

위 게시글에서 더 자세하고 좋은 정보를 얻을 수 있다.

4bit의 데이터를 처리하여 7bit의 output이 나온다.

728x90

반응형

'HW Design Study > NPU' 카테고리의 다른 글

| [DPU] DPU Block 공부하기 - (2) (0) | 2024.03.21 |

|---|---|

| [DPU] DPU Block 공부하기 - (1) (0) | 2024.03.18 |