반응형

- 예제를 통해 테스트벤치 작성

- 가능한 모든 input 조합을 전부 생성할 예정

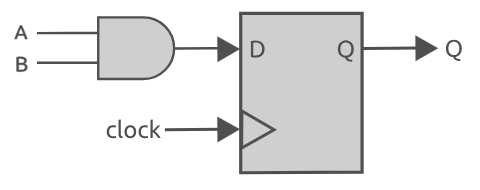

- 회로 분석

- 2 inputs

- AND gate

- D ff

1. Create a Testbench Module

- 테스트벤치 코드가 들어갈 빈 모듈을 선언

- 테스트벤치 모듈의 이름 선언에 대해...

- design 이름과 비슷하게 선언

- design 이름 끝에 _tb, _test 를 추가

- 테스트벤치 모듈의 이름 선언에 대해...

module example_tb ();

// code here

endmodule : example_tb2. Instanitate the DUT

- 작업할 수 있는 빈 테스트벤치 모듈이 생겼다.

- 테스트할 design을 인스턴스화.

- positional instantiation보다 named instantiation이 쉽다.

example_design dut (

.clock (clk), // clock port에 clk signal을 끼우겠다.

.reset (reset), // reset port에 reset signal을 끼우겠다.

.a (in_a), // a port에 in_a signal을 끼우겠다.

.b (in_b), // b port에 in_b signal을 끼우겠다.

.q (out_q) // q port에 out_q signal을 끼우겠다.

);3. Generate the Clock and Reset

- 둘 다 initial block에서 생성 가능.

- delay module로 상태 변화 스케쥴.

- clock signal

forever키워드 사용- 매 1ns마다 inversion을 스케쥴.

- => clock frequency == 500MHz

- 실제 FPGA는 500MHz 내기 힘들다.

- 하드웨어의 주파수와 일치해야함.

- 실제 FPGA는 500MHz 내기 힘들다.

// generate the clock

initial begin

clk = 1'b0;

forever #1 clk = ~clk;

end

// generate the reset

initial begin

reset = 1'b1;

#10

reset = 1'b0;

end4. Write the Stimulus

- 마지막 단계

- test stimulus 작성

- 한 턴에 4가지 경우의 수 (2 input이니까)를 생성해야 함.

- 신호 전파 지연 시간도 고려해야 함.

- input을 변수로 할당.

- 이후 delay Operaor 이용

- inputs, output에 대한 모니터링도 진행

- $monitor 이용

initial begin

// FPGA IO를 모니터링

$monitor("time = %3d, in_a = %b, in_b = %b, q = %2b \n", $time, in_a, in_b, q);

// input을 20ns 의 delay로 생성

in_a = 1'b0;

in_b = 1'b0;

#20

in_a = 1'b1;

#20

in_a = 1'b0;

in_b = 1'b1;

#20

in_a = 1'b1;

end- 사실 K-map 형태 (00, 01, 11, 10)를 차용하면 코드 1줄을 더 줄일 수 있다.

Full Example Code

`timescale 1ns / 1ps

module example_tb ();

// clock, reset 신호

reg clk;

reg reset;

// IO

reg in_a;

reg in_b;

wire out_q;

// DUT 인스턴스화

example_design dut (

.clock (clk),

.reset (reset),

.a (in_a),

.b (in_b),

.q (out_q)

);

// clock 생성

initial begin

clk = 1'b0;

forever #1 clk = ~clk;

end

// reset 생성

initial begin

reset = 1'b1;

#10

reset = 1'b0;

end

// Test stimulus

initial begin

// FPGA IO를 모니터링

$monitor("time = %3d, in_a = %b, in_b = %b, q = %2b \n", $time, in_a, in_b, q);

// input을 20ns 의 delay로 생성

in_a = 1'b0;

in_b = 1'b0;

#20

in_a = 1'b1;

#20

in_a = 1'b0;

in_b = 1'b1;

#20

in_a = 1'b1;

end

endmodule : example_tb반응형

'Verilog HDL > 1. Verilog HDL Basic (문법)' 카테고리의 다른 글

| [Statement] 1. if문 (0) | 2024.01.13 |

|---|---|

| [Testbench] 8. 예제 풀이 (0) | 2024.01.13 |

| [Testbench] 6. System Tasks (0) | 2024.01.13 |

| [Testbench] 5. forever loop (0) | 2024.01.13 |

| [Testbench] 4. initial block (0) | 2024.01.13 |