디지털 공학의 clock은 중요하다. sequential logic은 clock 없이는 구동되지 않는다. Clock은 디지털 회로의 동작을 synchronize 하고, data의 전송, 처리의 timing을 제어한다.

Clock?

clock은 주기적인 신호이다. Sequential logic에서 timing을 제공한다. 일반적으로 square wave의 형태를 가지며 1과 0 즉, High와 Low를 반복하는 상태를 갖는다.

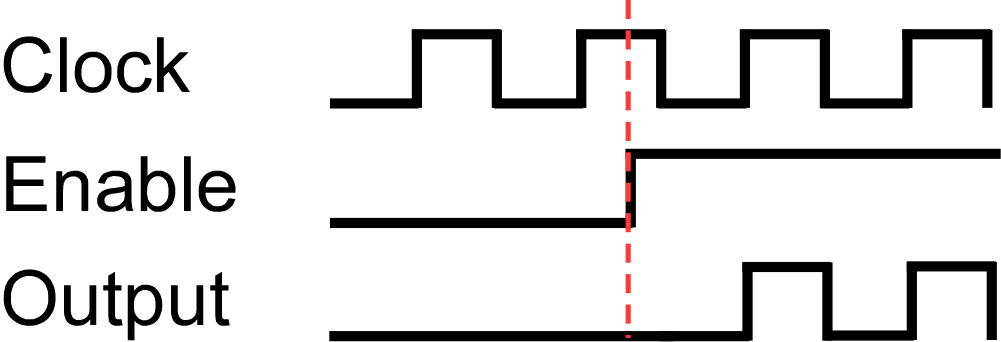

[그림 1]은 clock waveform을 보여주는데, square wave 형태이다.

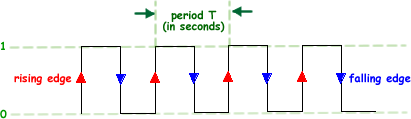

또한, [그림 2]를 통해 clock을 더 이해할 수 있다. clock cycle(period T)은 한 rising edge (posedge)에서 다음 rising edge까지의 시간이다. frequency는 clock 신호가 반복되는 횟수이다. 단위는 Hz(헤르츠)인데, 60Hz는 1초당 60번의 clock 신호가 나온다는 뜻이다.

Rising Edge vs Falling Edge

Rising Edge 즉, Verilog에서 posedge로 표현하는 Edge는 [그림 2]에서 볼 수 있듯, 0에서 1로 clock이 Toggle할 때를 의미한다. rising edge 상황에서 회로가 동작을 수행하는 것을 Anode type 회로라고 한다.

Falling Edge는 Rising Edge와 완전히 반대라고 할 수 있다. 1에서 0으로 Toggle 할 때를 의미한다. Verilog에서 negedge로 표현한다. falling edge 상황에서 회로가 동작을 수행하는 것을 Cathode type 회로라고 한다.

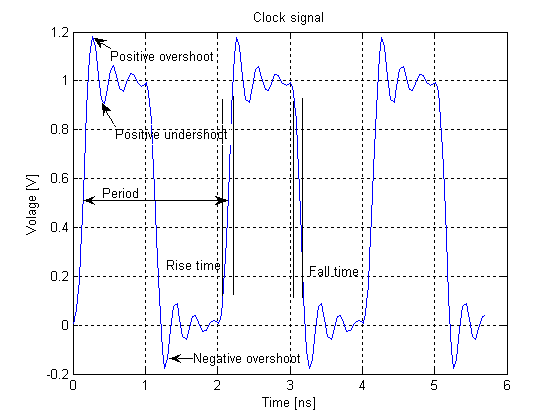

그럼 무슨 Type이 유리할까? ideal condition에서는 clock이 toggle되는 순간, 0과 1이 공존한다. 하지만, 현실에서 신호는 공존할 수 없다. [그림 3]은 현실에서의 신호를 나타낸다. 신호가 완벽한 square wave가 아닌 noise가 있는 점도 살펴볼 수 있다.

[그림 3]에서는 뚜렷하게 확인하기 어렵지만, 대부분의 condition에서 Rise time이 Fall time보다 길게 관측된다.

ideal condition에서 Rise time = Fall time = 0 (공존)이기에, 더 ideal에 가까운 Falling Edge를 Powerful 하게 사용할 수 있다.

즉, Cathode type이 일반적으로 더 유리하다고 할 수 있다. 물론 logic의 상황에 따라 다르다.

Clock의 역할

1. 동기화 (Synchronization)

Clock은 회로 내의 모든 logic 요소가 동시에 동작하도록 동기화한다. 이를 통해 데이터는 정확한 타이밍에 전송되고 처리된다.

2. 순서화 (Sequencing)

Clock은 순차적인 logic 요소, 예를 들어 F/F, reg, counter 등의 동작 순서를 제어한다.

3. Timing 제어

Clock은 데이터가 언제 Sampling 되고, 언제 전송되어야 하는지 등의 timing을 제어한다.

'Electronics > Digital Engineering' 카테고리의 다른 글

| Ch 5-1 Sequential circuits (0) | 2023.09.14 |

|---|---|

| Ch 5. Synchronous Sequential Logic (0) | 2023.09.14 |