Verilog에서 module의 용도는?

- We use modules to define the behavior of a compoenet in verilog

Verilog module에서 parameter의 용도는?

- We can use parameters to configure the behavior of our module when we instantiate it

Port의 세 가지 type은?

- input

- output

- inout

reg type과 wire type의 차이점은?

- The reg type can drive data and store valuse wheras the wire type can't

named와 positional instantiation의 차이점은? 무엇이 더 쉽나? 이유는?

- We use an ordered list to connect ports when using positional instantiation. We have to explicitly define the port we are connecting to when we use named instantiation.

- Named instantiation is easier to maintain as the code is not affected if we change the order of the ports in the module declaration.

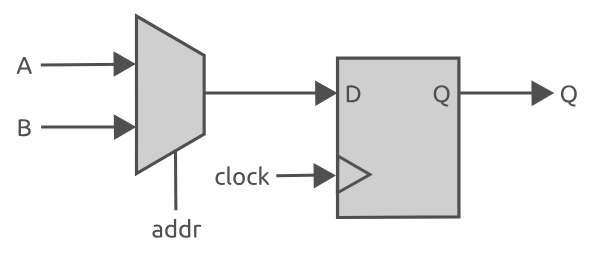

아래 그림의 회로에 대한 모듈을 선언하시오. (1995 표준과 2001 표준 둘 다)

```

// 2001 standard

module mux_ff (

input clock,

input a,

input b,

input addr,

output reg Q

);

// 1995 standard

module mux_ff (

clock,

a,

b,

addr,

q

);

input clock;

input a;

input b;

input addr;

output reg q;

endmodule

```

'HW Design > 1. Verilog HDL Basic' 카테고리의 다른 글

| [Verilog Data Types and Arrays] 1. Data 표현 (1) | 2024.01.02 |

|---|---|

| [Verilog Tutorial] Level-1 Basic Verilog Module 모음 (1) | 2024.01.02 |

| [Basic Verilog Module] 3. 베릴로그 모듈 예시 (2) | 2024.01.02 |

| [Basic Verilog Module] 2. 모듈 인스턴스화 (2) | 2024.01.02 |

| [Basic Verilog Module] 1. Verilog 의 구조 (0) | 2023.12.31 |