Module Instantiation

Instantiation 번역하면 인스턴스화입니다. 용어는 생소할 수 있으나, 그렇게 어렵지 않은 개념입니다.

그러나, Verilog를 함에 있어 Instantiation을 모르거나 개념을 잘 잡지 못한다면

큰 불이익이 있을 정도로 중요한 개념입니다.

Instantiation

Instantiation은 이미 작성한 Verilog Module을 호출하는 과정입니다.

호출이 중요한 Key point인데, C 언어 혹은 Python 등의 다른 언어에서 함수를 호출하는 것과 비슷합니다.

- Calling function in SW languages

1. 함수 선언 (input 변수, return 값, 함수 이름, 동작 등)

2. 함수 호출

SW languages에서 함수를 호출하는 과정입니다. 심플하죠.

Verilog는 HDL인 만큼 함수 호출과 Instantiation이 완전히 같지는 않습니다.

아래에 자세히 서술하겠습니다.

Instance

Instance는 Instantiation된 모든 module을 지칭합니다.

가령 add.v 파일에 add라는 덧셈기 모듈을 만들었다고 해봅시다.

top.v 파일은 가장 넓은 범위의 모듈인데, 이 top.v에서 add 모듈을 사용해야 합니다.

이 때 top.v에 호출된 add 모듈을 Instance module 이라고 지칭합니다.

이 Instance를 통해 복잡한 design을 만들 수 있습니다.

여러 하위 모듈을 상위 모듈에 Instantiation 하는 것이죠.

전자 회로

Instantiation을 회로에 빗대어 보겠습니다.

기존 전자 회로를 고안할 때, 브레드보드에 IC 칩을 끼우고 wire를 연결합니다.

IC칩을 생각해볼까요? IC칩은 저희가 만든 회로가 아닙니다.

IC 내부의 회로를 사용하고 싶어 가져와서 배치하는 것이죠.

이 배치하는 과정이 Instantiation 이라고 생각할 수 있습니다.

그럼 브레드보드에 배치된 IC칩은 Instance가 될 것입니다.

System flow

위 내용을 정리하고 System Design에 적용한 내용을 요약하면 아래와 같습니다.

- design에 필요한 모든 인스턴스 생성

- 인스턴스들을 연결하여 완전한 시스템 만들기

- 전자 시스템에서 컴포넌트를 배선(wiring) 하는 것과 같다.

Two methods of Instantiation

Instantiation을 하는 방법은 두 가지가 있습니다. 두 방법은 아래와 같습니다.

- Named instantiation

- Positional instantiation

- Verilog 2001 standard에서는 둘 다 사용 가능

- Verilog 1995 standard는 positional instantiation 만 사용 가능

Positional Module Instantiation

- 모듈 포트를 연결하기 위해 list를 사용

- list의 순서는 모듈에서 포트가 선언된 순서와 일치해야 함.

- 예를 들어, clock을 먼저 선언하고 reset을 선언하는 경우 -> clock 신호를 module IO에 먼저 연결해야 함.

- positional instantiation example

<module_name> # ( // Parameters를 쓸 경우, 여기에서 연결 <parameter_value> ) <instance_name> ( // 모듈 포트 연결 <signal_name>, // 먼저 선언된 포트에 연결 (clock) <signal_name> // 이후 선언된 포트에 연결 (reset) );- - 선언한 모듈의 이름과 같아야 함

- - instantiated module의 특정 이름

- 디자인이 발전함에 따라 포트의 순서가 변경될 수 있음.

- => 유지가 어렵다.

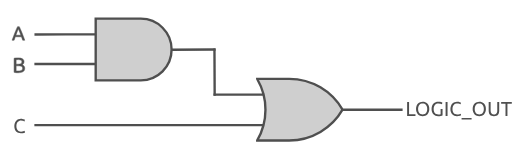

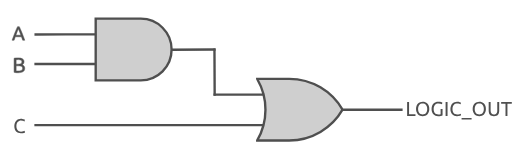

example module

example module - 모듈의 포트 선언 순서 중요

// 모듈 포트 선언 and_or ( input a, input b, input c, output logic_out );- Positional instantiation 을 이용하여 모듈 인스턴스 생성

// 모듈 인스턴스 생성 // positional instantiation 예제 and_or example_and_or ( in_a, in_b, in_c, and_or_out );

Named Module Instantiation

- 신호를 연결할 포트의 이름을 명시적으로 정의함

- 포트 선언 순서는 중요하지 않음

- 일반적으로 postional instantiation 보다 선호

- 읽기 쉽고, 이해하기 쉬운 코드 생성

- 포트 순서를 신경쓰지 않아, 포트를 수정할 수 있으므로 유지 관리가 쉽다.

- named module instantiation

- 일반적인 구문

<module_name> # ( // parameters는 여기에서 연결 .<parameter_name> (<parameter_value>) ) <instance_name> ( // 모듈 포트에 연결 .<port_name> (<signal_name>), .<port_name> (<signal_name>) );- <module_name>, <parameter_name>, <port_name> 은 모듈을 정의할 때 사용한 이름과 일치해야 함.

// 모듈 포트 선언 and_or ( input a, input b, input c, output logic_out );

// 모듈 인스턴스 생성

// named instantiation 예제

and_or example_and_or (

.a (in_a),

.b (in_b),

.c (in_c),

.logic_out (and_or_out)

);'Verilog HDL > 1. Verilog HDL Basic (문법)' 카테고리의 다른 글

| [Basic Verilog Module] 4. 예제 풀이 (1) | 2024.01.02 |

|---|---|

| [Basic Verilog Module] 3. 베릴로그 모듈 예시 (2) | 2024.01.02 |

| [Basic Verilog Module] 1. Verilog 의 구조 (0) | 2023.12.31 |

| [Verilog Tutorial] 1 - Introduction (2) | 2023.10.04 |

| [LINUX] 리눅스 기본 명령어 알아보기 (0) | 2023.09.28 |