2024.09.06 - [Project/16bit CPU Design] - [0] 프로젝트 개요

[0] 프로젝트 개요

8bit CPU를 설계하려 합니다. 목표는 이번 년도가 끝날 때까지 성공!https://www.youtube.com/watch?v=qJgsuQoy9bc위 유튜브 영상을 참고해서 6502를 만들어볼 생각입니다.C++ 공부에도 큰 도움이 될 것 같아요.목

han-pu.tistory.com

큰 일 났습니다..

사실 엄청 큰 일은 아니고 8bit CPU를 만들려했으나, 현재 듣고 있는 컴퓨터 구조 수업에서 굉장히 자세히 16bit 폰노이만 CPU HW 구조에 대해 알려주셔서...

16bit CPU를 만드는데에 성공하였습니다.

그래서 프로젝트 자체는 성공했으나, 위 개요에서처럼 착착 진행되진 않았고...

3시간동안 강의 듣고 한 3일정도 틈틈히 만드니까 뚝딱 완성!!

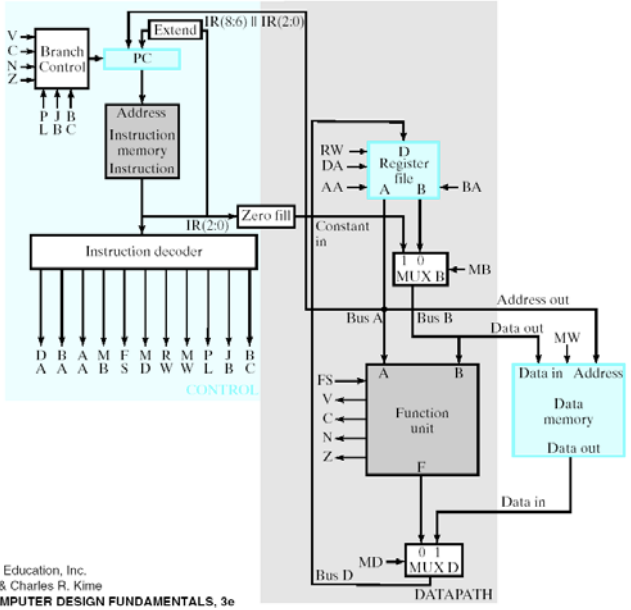

Architecture

현대 CPU의 가장 간단한 표현이다.

위 Block Diagram은 CPU의 대부분의 구조를 설명한다. 생각보다 간단하다.

그러나, 64bit ISA와 엄청난 양의 Reg, Mem이 있다면 말은 달라진다...

그럼에도 저 다이어그램으로 CPU 구현 및 동작 확인이 가능하니 이 글을 보시는 분들도 도전해보시길

이론적인 내용은 "Logic and computer design fundamentals - M.Morris..." 책의 Ch.6부터 공부하면 될 것이다.

아래는 구매 사이트 및 책 표지

https://www.aladin.co.kr/shop/wproduct.aspx?ItemId=57269383

Logic and Computer Design Fundamentals, Global Edition (Paperback, 5 ed)

Logic and Computer Design Fundamentals, Global Edition (Paperback, 5 ed)

www.aladin.co.kr

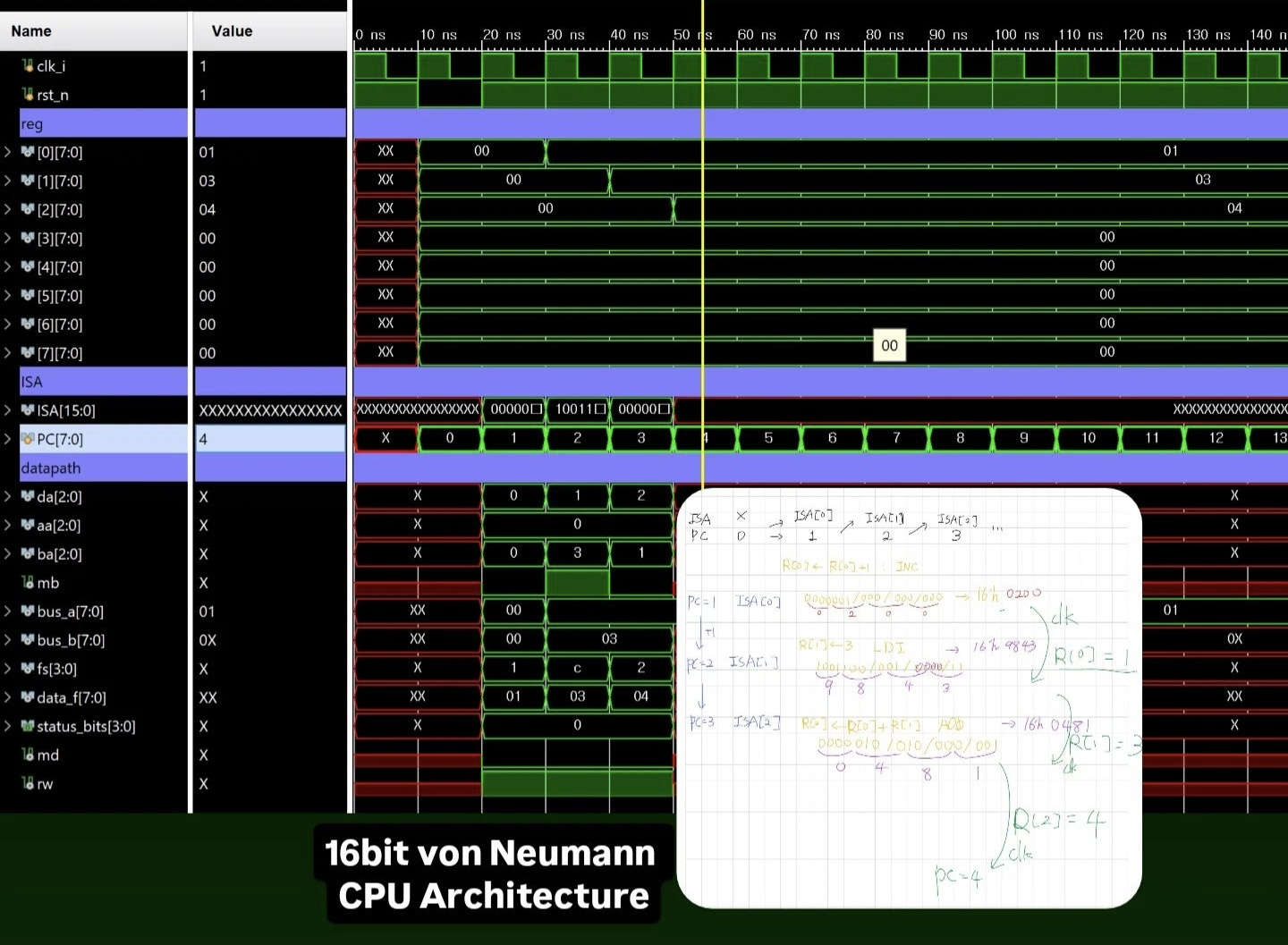

Waveform

Datapath Waveform

CPU ISA 동작 Waveform

ISA에 적힌 값을 한 줄씩 읽으면서 동작을 수행한다.

손연산 값에 맞게 waveform도 정상 작동한다.

SDK에 올려서 C언어 처럼 만들어볼 수도 있을 것 같다.

AXI4 Lite로 ISA를 넣어주면 될 듯

'Project > RISC-V CPU Architecture Design' 카테고리의 다른 글

| [2] 16bit CPU Design 이후 프로젝트 방향 feat. RISC-V (0) | 2024.11.15 |

|---|---|

| [0] 프로젝트 개요 (5) | 2024.09.06 |