디지털 설계?

Verilog 로 코드짜고 뚱땅 뚱땅 설계하는 일.

대충 설계 다 하면 공정에서 그대로 Chip이 나온다고 알고 있습니다.

ASIC World?

WELCOME TO WORLD OF ASIC

There just isn't a great source of detailed VLSI/DIGITAL information out there. If I actually keep this up, this should be it. However, unless people take an active interest and submit some ideas, tutorials, examples, may be some cores etc., it may die ver

www.asic-world.com

베릴로그 알려주고...

예제도 주고...

질문 답변도 해주는 사이트 입니다. 참고하십셔

직무 분석

ASIC World에 글 하나 올라왔습니다.

언제 올라온진 모르구요.

설명 보면 이러한 직군 뽑는데 아래 역량이 필요하다. 이런 느낌이구요.

한번 분석해봅시다.

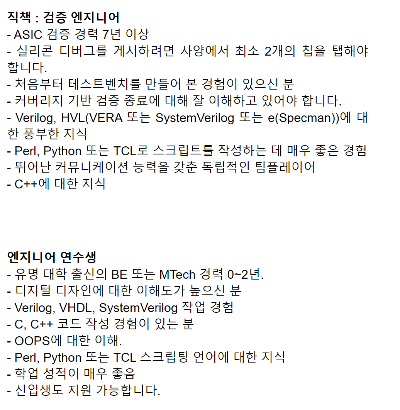

Verification Engineer

검증 엔지니어

머 테스트벤치 코드 짜고 이런 것 같습니다.

Verilog 보다는 System Verilog등의 좀 더 high level 언어에서 tb 코드를 많이 짜는걸로 알고있고요.

필요 역량 한번 볼까요

- 7년 경력

: 할말이 없네요. 경력 열심히 쌓고

- 최소 2개의 Chip을 (영어로도 tapped)

: 무슨뜻인지 모르겠습니다.

- 테스트 벤치 경험

: 검증 엔지니어니까 당연하겠죠.

- Verilog, HVL(VERA, SystemVerilog, e)

: tb 언어 잘써야 합니다.

tb로 채택하는 언어에 VERA, e 등도 있었네요. 몰랐습니다.

- Perl, Python 또는 TCL로 스크립트를 작성해본 경험

: Python은 아는데 Perl, TCL은 처음보네요.

둘 다 언어입니다. 스크립트 라는 말은 또 정확히 모르겠습니다.

https://ko.wikipedia.org/wiki/Tcl : TCL 설명

- 팀워크

: 롤 열심히 하시구요.

- C++에 대한 지식

: 하드한 지식을 요구하진 않는 것 같습니다.

풍부한~ 이런거 없죠.

그래도 알아둬야하는 언어인 것 같습니다.

전 C++은 하나도 모르구요.

C 좀 하다 Python으로 넘어갔는데 어쩝니까 뭐...

Python 뿌시고 C, C++ 차례로 뿌실게요. 3년뒤에...

엔지니어 연수생

에. 인턴이 더 중요하죠 아무래도.

- 유명대학 출식, 학사 or 석사

: 화이팅

- 디지털 디자인 이해도

: 수업 열심히 들으시고요.

- Verilog, VHDL, SystemVerilog 경험

: 풍부한 ~ 이런거 없으니까 적당한 경험을 요하는 것 같습니다.

- C, C++ 코드 경험

: 없습니다. 만들어야죠.

- OOPS에 대한 이해.

: 이게 되게 놀랐습니다. 글을 쓴 이유??

객체 지향 프로그래밍을 배우는게 비단 SW의 영역이 아니더라구요.

OOP 수업을 찾아서 들어야겠습니다.

- Perl, Python 또는 TCL로 스크립트를 작성해본 경험

: 위 보십셔

- 학업 성적이 매우 좋음

: 수업 열심히 들으십셔

마무리

이러한 언어 능력을 요한다 하는걸 알아봤습니다.

Verilog만 잘해도 밥먹고는 살겠지만, 좀 더 step-up 하려면 저런거 해야하구요.

OOP 수업 들으러 가보겠습니다.